# 5. DSP Blocks in Stratix III Devices

## Introduction

The Stratix<sup>®</sup> III family of devices have dedicated high-performance digital signal processing (DSP) blocks optimized for DSP applications. These DSP blocks of the Altera<sup>®</sup> Stratix device family are the third generation of hardwired, fixed function silicon blocks dedicated to maximizing signal processing capability, ease of use, and lowest silicon cost.

Many complex systems such as WiMAX, 3GPP WCDMA, high-performance computing (HPC), voice over Internet protocol (VoIP), H.264 video compression, medical imaging, and HDTV use sophisticated digital signal processing techniques, and this typically requires a large number of mathematical computations. Stratix III devices are ideally suited as the DSP blocks consist of a combination of dedicated elements that perform multiplication, addition, subtraction, accumulation, summation, and dynamic shift operations. Along with the high-performance Stratix III soft logic fabric and TriMatrix<sup>™</sup> memory structures, you can configure these blocks to build sophisticated fixed-point and floating-point arithmetic functions. These can be manipulated easily to implement common larger computationally intensive subsystems such as finite impulse response (FIR) filters, complex FIR filters, infinite impulse response (IIR) filters, fast Fourier transform (FFT) functions, and discrete cosine transform (DCT) functions.

### **DSP Block Overview**

Each Stratix III device has two to seven columns of DSP blocks that implement multiplication, multiply-add, multiply-accumulate (MAC), and dynamic shift functions efficiently. The logical functionality of the Stratix III DSP block is a superset of the previous generation of the DSP block found in Stratix and Stratix II devices.

Architectural highlights of the Stratix III DSP block include:

- High-performance, power-optimized, fully registered and pipelined multiplication operations

- Natively supported 9-bit, 12-bit, 18-bit, and 36-bit wordlengths

- Natively supported 18-bit complex multiplications

- Efficiently supported floating-point arithmetic formats (24-bit for single precision and 53-bit for double precision)

- Signed and unsigned input support

- Built-in addition, subtraction, and accumulation units to combine multiplication results efficiently

- Cascading 18-bit input bus to form tap-delay line for filtering applications

- Cascading 44-bit output bus to propagate output results from one block to the next block without external logic support

- Rich and flexible arithmetic rounding and saturation units

The second-stage and output registers are triggered by the positive edge of the clock signal and are cleared on power up. The following DSP block signals control the output registers within the DSP block:

- clock[3..0]

- ena[3..0]

- aclr[3..0]

# **Operational Mode Descriptions**

The various modes of operation are discussed below.

#### **Independent Multiplier Modes**

In independent input and output multiplier mode, the DSP block performs individual multiplication operations for general-purpose multipliers.

### 9-, 12-, and 18-Bit Multiplier

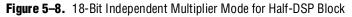

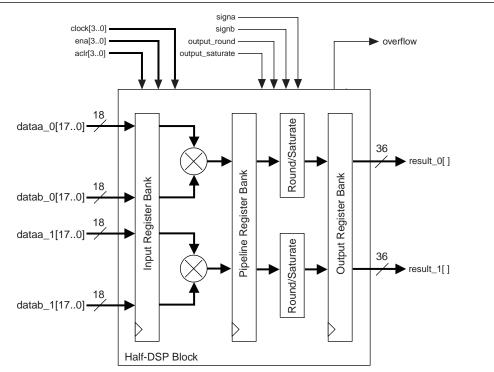

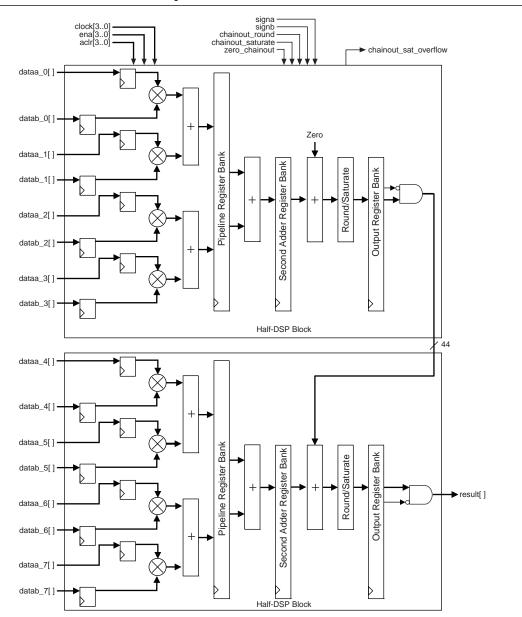

You can configure each DSP block multiplier for 9-, 12-, or 18-bit multiplication. A single DSP block can support up to eight individual  $9 \times 9$  multipliers, six  $12 \times 12$  multipliers, or up to four individual  $18 \times 18$  multipliers. For operand widths up to 9 bits, a  $9 \times 9$  multiplier is implemented. For operand widths from 10 to 12 bits, a  $12 \times 12$  multiplier is implemented, and for operand widths from 13 to 18 bits, an  $18 \times 18$  multiplier is implemented. This is done by the Quartus II software by zero-padding the LSBs. Figure 5–8, Figure 5–9, and Figure 5–10 show the DSP block in the independent multiplier operation mode.

#### **FFT Example**

The Fast Fourier Transform (FFT) is a very common DSP function used to convert samples in the time domain to and from the frequency domain. A fundamental building block of the FFT is the FFT butterfly. FFTs are most efficient when operating on complex samples. You can use the Stratix III DSP block to form the core of a complex FFT butterfly very efficiently.

#### 芯片详细信息

Manufacturer Part Number: EP3CLS100F484I7N

Package Description: LEAD FREE, FBGA-484

Manufacturer: Intel Corporation

JESD-609 Code: e1

Number of Inputs: 278

Operating Temperature-Max: 100 °C

Package Code: BGA

Peak Reflow Temperature (Cel): 260

Seated Height-Max: 2.15 mm

Supply Voltage-Nom: 1.2 V

Terminal Finish: Tin/Silver/Copper (Sn/Ag/Cu)

Time@Peak Reflow Temperature-Max (s): 40 Rohs Code: Ves

Reach Compliance Code: compliant

Risk Rank: 5.26

Length: 23 mm

Number of Logic Cells: 100448

Operating Temperature-Min: -40 °C

Package Equivalence Code: BGA484,22X22,40

Power Supplies: 1.2,1.2/3.3,2.5 V

Subcategory: Field Programmable Gate Arrays

Surface Mount: YES

Terminal Form: BALL

Width: 23 mm Part Life Cycle Code: Active

ECCN Code: 3A991

Clock Frequency-Max: 450 MHz

Moisture Sensitivity Level: 3

Number of Outputs: 278

Organization: 100448 CLBS

Package Shape:

SQUARE

Programmable Logic Type: FIELD PROGRAMMABLE GATE ARRAY

Supply Voltage-Max: 1.25 V

Technology: CMOS

Terminal Pitch: 1 mm Ihs Manufacturer: INTEL CORP

HTS Code: 8542.39.00.01

JESD-30 Code: S-PBGA-B484

Number of CLBs: 100448

Number of Terminals: 484

Package Body Material: PLASTIC/EPOXY

Package Style: GRID ARRAY

Qualification Status: Not Qualified

Supply Voltage-Min: 1.15 V

Temperature Grade: INDUSTRIAL

Terminal Position: BOTTOM

Chapter 6: Clock Networks and PLLs in Stratix III Devices Chapter Revision History

| 产品种类:                | FPGA - 现场可编程门阵列                      |  |

|----------------------|--------------------------------------|--|

| RoHS:                | RoHS 详细信息                            |  |

| 产品:                  | Cyclone III LS                       |  |

| 系列:                  | Cyclone III EP3CLS100                |  |

| 逻辑元件数量:              | 100448 LE                            |  |

| 自适应逻辑模块 - ALM:       | 2                                    |  |

| 嵌入式内存:               | 4.25 Mbit                            |  |

| 输入/输出端数量:            | 294 I/O                              |  |

| 工作电源电压:              | 1.15 V to 1.25 V                     |  |

| 最小工作温度:              | - 40 C                               |  |

| 最大工作温度:              | + 85 C                               |  |

| 安装风格:                | SMD/SMT                              |  |

| 封装 / 箱体:             | FBGA-484                             |  |

| 封装:                  | Tray                                 |  |

| 商标:                  | Intel / Altera                       |  |

| 最大工作频率:              | 274 MHz                              |  |

| 湿度敏感性:               | Yes                                  |  |

| 逻辑数组块数量——LAB:        | 6278 LAB                             |  |

| 产 <mark>品类型</mark> : | FPGA - Field Programmable Gate Array |  |

| 工厂包装数量:              | 60                                   |  |

| 子类别:                 | Programmable Logic ICs               |  |

| 总内存:                 | 4451328 bit                          |  |

| 商标名:                 | Cyclone III                          |  |

| 零件号别名:               | 970796                               |  |