# **Configuration Details**

### **Configuration Memory Frames**

Virtex®-5 FPGA configuration memory is arranged in frames that are tiled about the device. These frames are the smallest addressable segments of the Virtex-5 configuration memory space, and all operations must therefore act upon whole configuration frames. Virtex-5 frame counts and configuration sizes are shown in Table 6-1. Depending on BitGen options, additional overhead exists in the configuration bitstream. The exact bitstream length is available in the rawbits file (.rbt) created by using the "-b" option with bitgen or selecting "Create ASCII Configuration File" in the Generate Programming File options popup in ISE. Bitstream length (words) are roughly equal to the configuration array size (words) plus configuration overhead (words). Bitstream length (bits) are roughly equal to the bitstream length in words times 32.

Table 6-1: Virtex-5 Device Frame Count, Frame Length, Overhead, and Bitstream Size

| Device | Non-Configuration Frames <sup>(1)</sup> | Configuration<br>Frames | Total Device<br>Frames | Frame Lengths in Words (2) | Configuration Array<br>Size in Words <sup>(3)</sup> | Bitstream Overhead in Words <sup>(4)</sup> |

|--------|-----------------------------------------|-------------------------|------------------------|----------------------------|-----------------------------------------------------|--------------------------------------------|

| LX30   | 172                                     | 6,376                   | 6,548                  | 41                         | 261,416                                             | 272                                        |

| LX50   | 258                                     | 9,564                   | 9,822                  | 41                         | 392,124                                             | 272                                        |

| LX85   | 426                                     | 16,644                  | 17,070                 | 41                         | 682,404                                             | 272                                        |

| LX110  | 568                                     | 22,192                  | 22,760                 | 41                         | 909,872                                             | 272                                        |

| LX155  | 800                                     | 32,544                  | 33,344                 | 41                         | 1,334,304                                           | 272                                        |

| LX220  | 1,040                                   | 40,496                  | 41,536                 | 41                         | 1,660,336                                           | 272                                        |

| LX330  | 1,560                                   | 60,744                  | 62,304                 | 41                         | 2,490,504                                           | 272                                        |

| LX20T  | 126                                     | 3,762                   | 3,888                  | 41                         | 154,242                                             | 272                                        |

| LX30T  | 184                                     | 7,136                   | 7,320                  | 41                         | 292,576                                             | 272                                        |

| LX50T  | 276                                     | 10,704                  | 10,980                 | 41                         | 438,864                                             | 272                                        |

| LX85T  | 444                                     | 17,784                  | 18,228                 | 41                         | 729,144                                             | 272                                        |

| LX110T | 592                                     | 23,712                  | 24,304                 | 41                         | 972,192                                             | 272                                        |

| LX155T | 808                                     | 32,800                  | 33,608                 | 41                         | 1,344,800                                           | 272                                        |

| LX220T | 1,064                                   | 42,016                  | 43,080                 | 41                         | 1,722,656                                           | 272                                        |

| LX330T | 1,596                                   | 63,024                  | 64,620                 | 41                         | 2,583,984                                           | 272                                        |

| SX35T  | 244                                     | 10,168                  | 10,412                 | 41                         | 416,888                                             | 272                                        |

| SX50T  | 366                                     | 15,252                  | 15,618                 | 41                         | 625,332                                             | 272                                        |

Table 6-1: Virtex-5 Device Frame Count, Frame Length, Overhead, and Bitstream Size (Continued)

| Device | Non-Configuration Frames <sup>(1)</sup> | Configuration<br>Frames | Total Device<br>Frames | Frame Lengths in Words (2) | Configuration Array<br>Size in Words <sup>(3)</sup> | Bitstream Overhead in Words (4) |

|--------|-----------------------------------------|-------------------------|------------------------|----------------------------|-----------------------------------------------------|---------------------------------|

| SX95T  | 648                                     | 27,216                  | 27,864                 | 41                         | 1,115,856                                           | 272                             |

| SX240T | 1,440                                   | 60,672                  | 62,112                 | 41                         | 2,487,552                                           | 272                             |

| FX30T  | 244                                     | 10,296                  | 10,540                 | 41                         | 422,136                                             | 272                             |

| FX70T  | 488                                     | 20,592                  | 21,080                 | 41                         | 844,272                                             | 272                             |

| FX100T | 696                                     | 30,016                  | 30,712                 | 41                         | 1,230,656                                           | 272                             |

| FX130T | 870                                     | 37,520                  | 38,390                 | 41                         | 1,538,320                                           | 272                             |

| FX200T | 1,236                                   | 54,000                  | 55,236                 | 41                         | 2,214,000                                           | 272                             |

| TX150T | 810                                     | 32,980                  | 33,790                 | 41                         | 1,352,180                                           | 272                             |

| TX240T | 1,236                                   | 50,112                  | 51,348                 | 41                         | 2,054,592                                           | 272                             |

<sup>1.</sup> Non-configuration frames do not contribute to the bitstream size.

## **Configuration Registers**

All Virtex-5 FPGA bitstream commands are executed by reading or writing to the configuration registers.

#### Packet Types

The FPGA bitstream consists of two packet types: Type 1 and Type 2. These packet types and their usage are described below.

#### Type 1 Packet

The Type 1 packet is used for register reads and writes. Only 5 out of 14 register address bits are used in Virtex-5 FPGAs. The header section is always a 32-bit word.

Following the Type 1 packet header is the Type 1 Data section, which contains the number of 32-bit words specified by the word count portion of the header.

Table 6-2: Type 1 Packet Header Format

| Header<br>Type  | Oncode Register Addre |         | Reserved | Word Count |

|-----------------|-----------------------|---------|----------|------------|

| [31:29] [28:27] |                       | [26:13] | [12:11]  | [10:0]     |

| 001             | 001 xx RRRRRRRRxxxxx  |         | RR       | xxxxxxxxxx |

#### Notes:

1. "R" means the bit is not used and reserved for future use.

<sup>2.</sup> All Virtex-5 configuration frames consist of 41 32-bit words.

<sup>3.</sup> Configuration array size equals the number of configuration frames times the number of words per frame.

<sup>4.</sup> Configuration overhead consists of commands in the bitstream that are needed to perform configuration but do not themselves program any memory cells. Configuration overhead contributes to the overall bitstream size.

| 芯片详细信息                           |                                         |                                                                   |                               |

|----------------------------------|-----------------------------------------|-------------------------------------------------------------------|-------------------------------|

| Manufacturer Part Number:        | Pbfree Code:                            | Rohs Code:                                                        | Part Life Cycle Code:         |

| XC2V8000-6FFG1517C               |                                         |                                                                   | Obsolete                      |

| hs Manufacturer:                 | Part Package Code:                      | Package Description:                                              | Pin Count:                    |

| XILINX INC                       | BGA                                     | 40 X 40 MM, 1 MM PITCH, MS-<br>034AAU-1, FLIP CHIP, FBGA-<br>1517 | 1517                          |

| Reach Compliance Code:           | HTS Code:                               | Manufacturer:                                                     | Risk Rank:                    |

| not_compliant                    | 8542.39.00.01                           | Xilinx                                                            | 5.81                          |

| Clock Frequency-Max:             | Combinatorial Delay of a CLB-Max:       | JESD-30 Code:                                                     | JESD-609 Code:                |

| 820 MHz                          | 0.35 ns                                 | S-PBGA-B1517                                                      | e1                            |

| Length:                          | Moisture Sensitivity Level:             | Number of CLBs:                                                   | Number of Equivalent Gates:   |

| 40 mm                            | 4                                       | 11648                                                             | 8000000                       |

| Number of Terminals:             | Operating Temperature-Max:              | Organization:                                                     | Package Body Material:        |

| 1517                             | 85 °C                                   | 11648 CLBS, 8000000 GATES                                         | PLASTIC/EPOXY                 |

| Package Code:                    | Package Shape:                          | Package Style:                                                    | Peak Reflow Temperature (Cel) |

| BGA                              | SQUARE                                  | GRID ARRAY                                                        | 245                           |

| Programmable Logic Type:         | Qualification Status:                   | Seated Height-Max:                                                | Supply Voltage-Max:           |

| FIELD PROGRAMMABLE<br>GATE ARRAY | Not Qualified                           | 3.4 mm                                                            | 1.575 V                       |

| Supply Voltage-Min:              | Supply Voltage-Nom:                     | Surface Mount                                                     | Technology:                   |

| 1.425 V                          | 1.5 V                                   | YES                                                               | CMOS                          |

| Temperature Grade:               | Terminal Finish:                        | Terminal Form:                                                    | Terminal Pitch:               |

| OTHER                            | Tin/Silver/Copper<br>(Sn95.5Ag4.0Cu0.5) | BALL                                                              | 1 mm                          |

| Terminal Position:               | Time@Peak Reflow Temperature-           | Width:                                                            |                               |

| BOTTOM                           | Max (s):                                | 40 mm                                                             |                               |

#### **Readback Capture**

The configuration memory readback command sequence is identical for both Readback Verify and Readback Capture. However, the Capture sequence requires an additional step to sample internal register values.

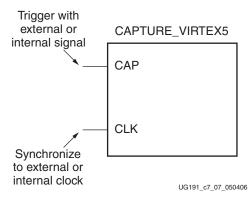

Users can sample block RAM outputs, and CLB and IOB registers by instantiating the CAPTURE\_VIRTEX5 primitive in their design (Figure 7-7) and asserting the CAP input on that primitive while the design is operating. On the next rising clock edge on the CAPTURE\_VIRTEX5 CLK input, the internal GRDBK signal is asserted, storing all CLB and IOB register values into configuration memory cells. These values can then be read out of the device along with the IOB and CLB configuration columns by reading configuration memory through the readback process. Register values are stored in the same memory cell that programs the register's init state configuration, thus sending the GRESTORE command to the Virtex-5 configuration logic after the Capture sequence can cause registers to return to an unintended state.

Alternatively, the GRDBK signal can be asserted by writing the GCAPTURE command to the CMD register. This command asserts the GRDBK signal for two CCLK or TCK cycles, depending on the startup clock setting.

Figure 7-7: Virtex-5 Device Library Primitive

| Table 7-8: ( | Capture : | Signals |

|--------------|-----------|---------|

|--------------|-----------|---------|

| Signal   | Description                                                                | Access                                                                                           |  |

|----------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| GCAPTURE | Captures the state of all slice and IOB registers. Complement of GRESTORE. | GCAPTURE command through the CMD register or <i>CAP</i> input on capture block, user controlled. |  |

| GRESTORE | Initializes all registers as configured.                                   | CMD register and STARTUP_VIRTEX5 block.                                                          |  |

If the CAP signal is left asserted over multiple clock cycles, the Capture cell is updated with the new register value on each rising clock edge. To limit the capture operation to the first rising clock edge, the user can add the ONESHOT attribute to the CAPTURE\_VIRTEX5 primitive. More information on the ONESHOT attribute can be found in the Constraints Guide.

Once the configuration memory frames have been read out of the device, the user can pick the captured register values out of the readback data stream. The capture bit locations are given in the logic allocation file (design.11) as described in Table 7-9.

| XC2S50-6FGG256I 2001+ |       | BGA      | 2315 |

|-----------------------|-------|----------|------|

| XC2S50-6FGG256C 2001+ |       | BGA      | 2315 |

| XC2S50-6FG456I        | 2001+ | BGA      | 2315 |

| XC2S50-6FG456C        | 2001+ | BGA      | 2315 |

| XC2S50-6FG256I        | 2001+ | BGA      | 2315 |

| XC2S50-6FG256C        | 2001+ | BGA      | 2315 |

| XC2S50-6CSG144I       | 2001+ | BGA      | 2315 |

| XC2S50-6CSG144C       | 2001+ | BGA      | 2315 |

| XC2S50-6CS144I        | 2001+ | BGA      | 2315 |

| XC2S50-6CS144C        | 2001+ | BGA      | 2315 |

| XC2S50-5VQG100I       | 2001+ | BGA      | 2315 |

| XC2S50-5VQG100C       | 2001+ | BGA      | 2315 |

| XC2S50-5VQ100I        | 2001+ | BGA      | 2315 |

| XC2S50-5VQ100C        | 2001+ | BGA      | 2315 |

| XC2S50-5TQG144I       | 2001+ | TQFP144  | 2315 |

| XC2S50-5TQG144C       | 2001+ | TQFP144  | 2315 |

| XC2S505TQG144C        | 2001+ | BGA      | 2315 |

| XC2S50-5TQC144C       | 2001+ | TQFP144  | 2315 |

| XC2S50-5TQ44I         | 2001+ | QFP      | 2315 |

| XC2S50-5TQ208         | 2001+ | QFP208   | 2315 |

| XC2S50-5TQ144I        | 2001+ | QFP      | 2315 |

| XC2S50-5TQ144I        | 2001+ | TQFP144  | 2315 |

| XC2S50-5TQ144C-ES     | 2001+ | QFP      | 2315 |

| XC2S50-5TQ144C        | 2001+ | TQFP144  | 2315 |

| XC2S50-5TQ144C        | 2001+ | TQFP144  | 2315 |

| XC2S505TQ144C         | 2001+ | BGA      | 2315 |

| XC2S50-5TQ144AMS      | 2001+ | QFP      | 2315 |

| XC2S50-5TQ144         | 2001+ | BGA      | 2315 |

| XC2S50-5TQ144         | 2001+ | TQFP     | 2315 |

| XC2S50-5T144C         | 2001+ | QFP      | 2315 |

| XC2S50-5PQG208I       | 2001+ | QFP208   | 2315 |

| XC2S50-5PQG208C       | 2001+ | QFP208   | 2315 |

| XC2S50-5PQG208C       | 2001+ | QFP      | 2315 |

| XC2S50-5PQG208C       | 2001+ | Stock    | 2315 |

| XC2S505PQG208C        | 2001+ | BGA      | 2315 |

| XC2S50-5PQG208AMS     | 2001+ | QFP144   | 2315 |

| XC2S50-5PQG208        | 2001+ | QFP208   | 2315 |

| XC2S50-5PQC208C       | 2001+ | QFP      | 2315 |

| XC2S50-5PQ210C        | 2001+ | QFP-210  | 2315 |

| XC2S50-5PQ208I        | 2001+ | BGA      | 2315 |

| XC2S50-5PQ208C-ES     | 2001+ | PQFP-208 | 2315 |