| Table 2–16. Stratix II Supported I/O Standards (Part 2 of 2) |                    |                                                    |                                                   |                                                |  |  |

|--------------------------------------------------------------|--------------------|----------------------------------------------------|---------------------------------------------------|------------------------------------------------|--|--|

| I/O Standard                                                 | Туре               | Input Reference<br>Voltage (V <sub>REF</sub> ) (V) | Output Supply<br>Voltage (V <sub>CCIO</sub> ) (V) | Board Termination Voltage ( $V_{TT}$ ) ( $V$ ) |  |  |

| SSTL-2 Class I and II                                        | Voltage-referenced | 1.25                                               | 2.5                                               | 1.25                                           |  |  |

## Notes to Table 2-16:

- (1) This I/O standard is only available on input and output column clock pins.

- (2) This I/O standard is only available on input clock pins and DQS pins in I/O banks 3, 4, 7, and 8, and output clock pins in I/O banks 9,10, 11, and 12.

- (3)  $V_{CCIO}$  is 3.3 V when using this I/O standard in input and output column clock pins (in I/O banks 9, 10, 11, and 12). The clock input pins supporting LVDS on banks 3, 4, 7, and 8 use  $V_{CCINT}$  for LVDS input operations and have no dependency on the  $V_{CCIO}$  level of the bank.

- (4) 1.2-V HSTL is only supported in I/O banks 4,7, and 8.

For more information on I/O standards supported by Stratix II I/O banks, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

Stratix II devices contain eight I/O banks and four enhanced PLL external clock output banks, as shown in Figure 2–57. The four I/O banks on the right and left of the device contain circuitry to support high-speed differential I/O for LVDS and HyperTransport inputs and outputs. These banks support all Stratix II I/O standards except PCI or PCI-X I/O pins, and SSTL-18 Class II and HSTL outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, enhanced PLL external clock output banks allow clock output capabilities such as differential support for SSTL and HSTL.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different  $V_{\text{CCIO}}$  level independently. Each bank also has dedicated VREF pins to support the voltage-referenced standards (such as SSTL-2). The PLL banks utilize the adjacent VREF group when voltage-referenced standards are implemented. For example, if an SSTL input is implemented in PLL bank 10, the voltage level at VREFB7 is the reference voltage level for the SSTL input.

I/O pins that reside in PLL banks 9 through 12 are powered by the VCC\_PLL<5, 6, 11, or 12>\_OUT pins, respectively. The EP2S60F484, EP2S60F780, EP2S90H484, EP2S90F780, and EP2S130F780 devices do not support PLLs 11 and 12. Therefore, any I/O pins that reside in bank 11 are powered by the VCCIO3 pin, and any I/O pins that reside in bank 12 are powered by the VCCIO8 pin.

Each I/O bank can support multiple standards with the same  $V_{CCIO}$  for input and output pins. Each bank can support one  $V_{REF}$  voltage level. For example, when  $V_{CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, and 3.3-V PCI for inputs and outputs.

## **On-Chip Termination**

Stratix II devices provide differential (for the LVDS or HyperTransport technology I/O standard), series, and parallel on-chip termination to reduce reflections and maintain signal integrity. On-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections.

Stratix II devices provide four types of termination:

- Differential termination (R<sub>D</sub>)

- Series termination (R<sub>S</sub>) without calibration

- Series termination (R<sub>S</sub>) with calibration

- Parallel termination (R<sub>T</sub>) with calibration

## **Dedicated Circuitry with DPA Support**

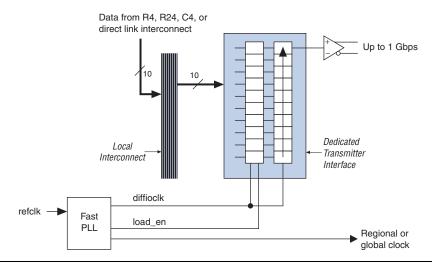

Stratix II devices support source-synchronous interfacing with LVDS or HyperTransport signaling at up to 1 Gbps. Stratix II devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by an integer factor W = 1 through 32. For example, a HyperTransport technology application where the data rate is 1,000 Mbps and the clock rate is 500 MHz would require that W be set to 2. The SERDES factor *J* determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor *J* can be set to 4, 5, 6, 7, 8, 9, or 10 and does not have to equal the PLL clock-multiplication W value. A design using the dynamic phase aligner also supports all of these *J* factor values. For a *J* factor of 1, the Stratix II device bypasses the SERDES block. For a *J* factor of 2, the Stratix II device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. Figure 2–58 shows the block diagram of the Stratix II transmitter channel.

Figure 2-58. Stratix II Transmitter Channel

Each Stratix II receiver channel features a DPA block for phase detection and selection, a SERDES, a synchronizer, and a data realigner circuit. You can bypass the dynamic phase aligner without affecting the basic source-synchronous operation of the channel. In addition, you can dynamically switch between using the DPA block or bypassing the block via a control signal from the logic array. Figure 2–59 shows the block diagram of the Stratix II receiver channel.

| 芯片详细信息                                                            |                        |                               |                                   |

|-------------------------------------------------------------------|------------------------|-------------------------------|-----------------------------------|

| Manufacturer Part Number:                                         | Rohs Code:             | Part Life Cycle Code:         | Ihs Manufacturer:                 |

| EP3C80F780C6N                                                     | Yes                    | Active                        | INTEL CORP                        |

| Package Description:                                              | Reach Compliance Code: | ECCN Code:                    | HTS Code:                         |

| 29 X 29 MM, 2.60 MM HEIGHT,<br>1 MM PITCH, LEAD FREE,<br>FBGA-780 | compliant              | 3A991                         | 8542.39.00.01                     |

| Manufacturer:                                                     | Risk Rank:             | Clock Frequency-Max:          | JESD-30 Code:                     |

| Intel Corporation                                                 | 5.29                   | 472.5 MHz                     | R-PBGA-B780                       |

| JESD-609 Code:                                                    | Length:                | Moisture Sensitivity Level:   | Number of CLBs:                   |

| e1                                                                | 29 mm                  | 3                             | 81264                             |

| Number of Inputs:                                                 | Number of Logic Cells: | Number of Outputs:            | Number of Terminals:              |

| 429                                                               | 81264                  | 429                           | 780                               |

| Operating Temperature-Max:                                        | Organization:          | Package Body Material:        | Package Code:                     |

| 85 °C                                                             | 81264 CLBS             | PLASTIC/EPOXY                 | BGA                               |

| Package Equivalence Code:                                         | Package Shape:         | Package Style:                | Peak Reflow Temperature (Cel):    |

| BGA780,28X28,40                                                   | RECTANGULAR            | GRID ARRAY                    | 245                               |

| Programmable Logic Type:                                          | Qualification Status:  | Seated Height-Max:            | Subcategory:                      |

| FIELD PROGRAMMABLE<br>GATE ARRAY                                  | Not Qualified          | 3.5 mm                        | Field Programmable Gate<br>Arrays |

| Supply Voltage-Max:                                               | Supply Voltage-Min:    | Supply Voltage-Nom:           | Surface Mount:                    |

| 1.25 V                                                            | 1.15 V                 | 1.2 V                         | YES                               |

| Technology:                                                       | Temperature Grade:     | Terminal Finish:              | Terminal Form:                    |

| CMOS                                                              | OTHER                  | Tin/Silver/Copper (Sn/Ag/Cu)  | BALL                              |

| Terminal Pitch:                                                   | Terminal Position:     | Time@Peak Reflow Temperature- | Width:                            |

| 1 mm                                                              | BOTTOM                 | Max (s):<br>40                | 29 mm                             |

| 产品种类:          | FPGA - 现场可编程门阵列                      |  |  |  |

|----------------|--------------------------------------|--|--|--|

| RoHS:          | RoHS 详细信息                            |  |  |  |

| 产品:            | Cyclone III                          |  |  |  |

| 系列:            | Cyclone III EP3C80                   |  |  |  |

| 逻辑元件数量:        | 81264 LE                             |  |  |  |

| 自适应逻辑模块 - ALM: | 12                                   |  |  |  |

| 嵌入式内存:         | 2.68 Mbit                            |  |  |  |

| 输入/输出端数量:      | 429 I/O                              |  |  |  |

| 工作电源电压:        | 1.15 V to 1.25 V                     |  |  |  |

| 最小工作温度:        | 0 C                                  |  |  |  |

| 最大工作温度:        | + 70 C                               |  |  |  |

| 安装风格:          | SMD/SMT                              |  |  |  |

| 封装/箱体:         | FBGA-780                             |  |  |  |

| 封装:            | Tray                                 |  |  |  |

| 商标:            | Intel / Altera                       |  |  |  |

| 最大工作频率:        | 315 MHz                              |  |  |  |

| 湿度敏感性:         | Yes                                  |  |  |  |

| 逻辑数组块数量——LAB:  | 5079 LAB                             |  |  |  |

| 产品类型:          | FPGA - Field Programmable Gate Array |  |  |  |

| 工厂包装数量:        | 36                                   |  |  |  |

| 子类别:           | Programmable Logic ICs               |  |  |  |

| 总内存:           | 2810880 bit                          |  |  |  |

| 商标名:           | Cyclone III                          |  |  |  |

| 零件号别名:         | 974350                               |  |  |  |