you need to support configuration input voltages of 1.8 V/1.5 V, you should set the VCCSEL to a logic high and the  $V_{CCIO}$  of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

## **Configuration Schemes**

You can load the configuration data for a Stratix II device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix II device. A configuration device can automatically configure a Stratix II device at system power-up.

You can configure multiple Stratix II devices in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

Stratix II FPGAs offer the following:

- Configuration data decompression to reduce configuration file storage

- Design security using configuration data encryption to protect your designs

- Remote system upgrades for remotely updating your Stratix II designs

Table 3–5 summarizes which configuration features can be used in each configuration scheme.

| Configuration Scheme | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |

|----------------------|--------------------------------------------------|-----------------|---------------|--------------------------|

| FPP                  | MAX II device or microprocessor and flash device | <b>√</b> (1)    | <b>√</b> (1)  | <b>✓</b>                 |

|                      | Enhanced configuration device                    |                 | <b>√</b> (2)  | <b>✓</b>                 |

| AS                   | Serial configuration device                      | <b>✓</b>        | ✓             | <b>√</b> (3)             |

| PS                   | MAX II device or microprocessor and flash device | <b>✓</b>        | ✓             | <b>✓</b>                 |

|                      | Enhanced configuration device                    | <b>✓</b>        | ✓             | <b>✓</b>                 |

|                      | Download cable (4)                               | ✓               | ✓             |                          |

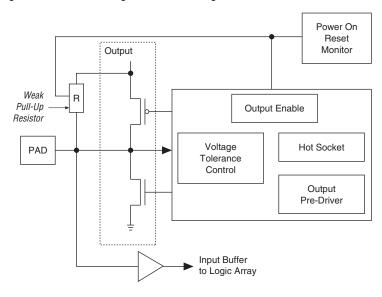

Figure 4–1. Hot Socketing Circuit Block Diagram for Stratix II Devices

The POR circuit monitors  $V_{CCINT}$  voltage level and keeps I/O pins tristated until the device is in user mode. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  is present to keep the I/O pins from floating. The 3.3-V tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  and/or  $V_{CCPD}$  are powered, and it prevents the I/O pins from driving out when the device is not in user mode. The hot socket circuit prevents I/O pins from internally powering  $V_{CCIO}$ ,  $V_{CCINT}$ , and  $V_{CCPD}$  when driven by external signals before the device is powered.

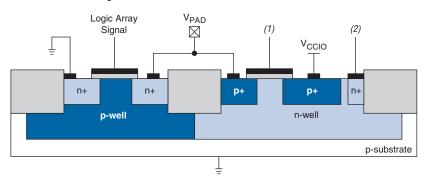

Figure 4–2 shows a transistor level cross section of the Stratix II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{\text{CCIO}}$  is powered before  $V_{\text{CCINT}}$  or if the I/O pad voltage is higher than  $V_{\text{CCIO}}$ . This also applies for sudden voltage spikes during hot insertion. There is no current path from signal I/O pins to  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  or  $V_{\text{CCPD}}$  during hot insertion. The  $V_{\text{PAD}}$  leakage current charges the 3.3-V tolerant circuit capacitance.

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

Notes to Figure 4-2:

- This is the logic array signal or the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

- This is the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

## Power-On Reset Circuitry

Stratix II devices have a POR circuit to keep the whole device system in reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$ ,  $V_{\rm CCIO}$ , and  $V_{\rm CCPD}$  voltage levels and tri-states all the user I/O pins while  $V_{\rm CC}$  is ramping up until normal user levels are reached. The POR circuitry also ensures that all eight I/O bank  $V_{\rm CCIO}$  voltages,  $V_{\rm CCPD}$  voltage, as well as the logic array  $V_{\rm CCINT}$  voltage, reach an acceptable level before configuration is triggered. After the Stratix II device enters user mode, the POR circuit continues to monitor the  $V_{\rm CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If there is a  $V_{\rm CCINT}$  voltage sag below the Stratix II operational level during user mode, the POR circuit resets the device.

When power is applied to a Stratix II device, a power-on-reset event occurs if  $V_{CC}$  reaches the recommended operating range within a certain period of time (specified as a maximum  $V_{CC}$  rise time). The maximum  $V_{CC}$  rise time for Stratix II device is 100 ms. Stratix II devices provide a dedicated input pin (PORSEL) to select POR delay times of 12 or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms. When the PORSEL pin is connected to  $V_{CC}$ , the POR time is 12 ms.

| 产品种类:          | FPGA - 现场可编程门阵列                      |  |  |

|----------------|--------------------------------------|--|--|

| RoHS:          | N                                    |  |  |

| 产品:            | Stratix II                           |  |  |

| 系列:            | Stratix II EP2S15                    |  |  |

| 逻辑元件数量:        | 15600 LE                             |  |  |

| 自适应逻辑模块 - ALM: | 6240 ALM                             |  |  |

| 嵌入式内存:         | 409.5 kbit                           |  |  |

| 输入/输出端数量:      | 366 I/O                              |  |  |

| 工作电源电压:        | 1.2 V                                |  |  |

| 最小工作温度:        | 0 C                                  |  |  |

| 最大工作温度:        | + 70 C                               |  |  |

| 安装风格:          | SMD/SMT                              |  |  |

| 封装/箱体:         | FBGA-672                             |  |  |

| 封装:            | Tray                                 |  |  |

| 商标:            | Intel / Altera                       |  |  |

| 湿度敏感性:         | Yes                                  |  |  |

| 逻辑数组块数量——LAB:  | 780 LAB                              |  |  |

| 工作电源电流: 250 mA |                                      |  |  |

| 产品类型:          | FPGA - Field Programmable Gate Array |  |  |

| 工厂包装数量:        | 40                                   |  |  |

| 子类别:           | Programmable Logic ICs               |  |  |

| 总内存:           | 419328 bit                           |  |  |

| 商标名:           | Stratix II                           |  |  |

| 零件号别名:         | 966856                               |  |  |

## 芯片详细信息 Manufacturer Part Number: Rohs Code: Part Life Cycle Code: Ihs Manufacturer EP2S15F672C5 O No Not Recommended INTEL CORP Package Description: Reach Compliance Code: ECCN Code: HTS Code 35 X 35 MM, 1 MM PITCH, compliant 3A991 8542.39.00.01 FBGA-672 Manufacturer. Risk Rank: Clock Frequency-Max: Combinatorial Delay of a CLB-Max: Intel Corporation 5.3 640 MHz 5.962 ns JESD-30 Code: JESD-609 Code: Length: Moisture Sensitivity Level: S-PBGA-B672 35 mm Number of CLBs: Number of Inputs: Number of Logic Cells: Number of Outputs: 6240 366 15600 358 Number of Terminals: Package Body Material: Operating Temperature-Max: Organization: 6240 CLBS PLASTIC/EPOXY 672 85 °C Package Code: Package Equivalence Code: Package Shape: Package Style: BGA BGA672.26X26.40 SQUARE GRID ARRAY Peak Reflow Temperature (Cel): Power Supplies: Programmable Logic Type: Qualification Status: FIELD PROGRAMMABLE 220 1.2,1.5/3.3,3.3 V Not Qualified **GATE ARRAY** Seated Height-Max: Subcategory: Supply Voltage-Max: Supply Voltage-Min: Field Programmable Gate 1.25 V 1.15 V Arrays Surface Mount: Temperature Grade: Supply Voltage-Nom: Technology: OTHER 1.2 V YES CMOS Terminal Finish: Terminal Form: Terminal Pitch: Terminal Position: BOTTOM TIN LEAD BALL 1.27 mm Time@Peak Reflow Temperature-Width: Max (s): 35 mm

30