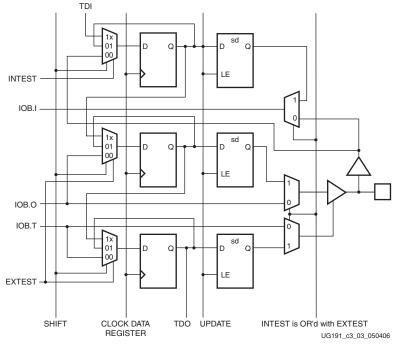

Figure 3-3: Virtex-5 Family Boundary-Scan Logic

### Bit Sequence Boundary-Scan Register

The order of each non-TAP IOB is described in this section. The input is first, then the output, and finally the 3-state IOB control. The 3-state IOB control is closest to the TDO. The input-only pins contribute only the input bit to the Boundary-Scan I/O data register. The bit sequence of the device is obtainable from the *Boundary-Scan Description Language Files* (BSDL files) for the Virtex-5 family. (These files can be obtained from the Xilinx software download area.) The bit sequence always has the same bit order and the same number of bits and is independent of the design.

## Instruction Register

The Instruction Register (IR) for the Virtex-5 device is connected between TDI and TDO during an instruction scan sequence. In preparation for an instruction scan sequence, the instruction register is parallel-loaded with a fixed instruction capture pattern. This pattern is shifted out onto TDO (LSB first), while an instruction is shifted into the instruction register from TDI.

To determine the operation to be invoked, an OPCODE necessary for the Virtex-5 Boundary-Scan instruction set is loaded into the Instruction Register. The length of the IR is device size-specific. The IR is 10 bits wide for the Virtex-5 LX, LXT, SXT, FXT, and TXT platform devices. The FX100T, FX130T, and FX200T have 14 bits of OPCODE because they contain 2 PowerPC processors. The 4 or 8 most significant bits support the PowerPC 440 embedded processor. The least significant 6 bits of the instruction code perform the same function for all Virtex-5 family members to support the new IEEE Standard 1532 for ISC devices. For PPC JTAG instruction, the least bits must be set to 100000 (20h). For PPC440 JTAG guidelines, refer to <u>UG200</u>, *Embedded Processor Block in Virtex-5 FPGAs Reference Guide*. Table 3-3 lists the available instructions for Virtex-5 devices.

| 产品种类:               | FPGA - 现场可编程门阵列                      |  |

|---------------------|--------------------------------------|--|

| 产品:                 | Virtex-II Pro                        |  |

| 系列:                 | XC2VP20                              |  |

| 逻辑元件数量:             | 20880 LE                             |  |

| 自适应逻辑模块 - ALM:      | 9280 ALM                             |  |

| 嵌入式内存:              | 1.55 Mbit                            |  |

| 输入/输出端数量:           | 404 I/O                              |  |

| 工作电源电压:             | 1.5 V                                |  |

| 最小工作温度:             | - 40 C                               |  |

| 最大工作温度:             | + 100 C                              |  |

| 安装风格:               | SMD/SMT                              |  |

| 封装 / 箱体:            | FBGA-676                             |  |

| 数据速率:               | 6.25 Gb/s                            |  |

| 商标:                 | Xilinx                               |  |

| 分布式RAM:             | 290 kbit                             |  |

| 内嵌式块RAM - EBR:      | 1584 kbit                            |  |

| 最大工作频率:             | 350 MHz                              |  |

| 湿度敏感性:              | Yes                                  |  |

| 逻辑数组块数量——LAB:       | 2320 LAB                             |  |

| 收发器数量:              | 8 Transceiver                        |  |

| 产 <mark>品类型:</mark> | FPGA - Field Programmable Gate Array |  |

| 工厂包装数量:             | 1                                    |  |

| 子类别:                | Programmable Logic ICs               |  |

| 商标名:                | Virtex                               |  |

#### 芯片详细信息

Manufacturer Part Number: XC2VP20-6FG676I

Ihs Manufacturer: XILINX INC

Reach Compliance Code: not\_compliant

Manufacturer: Xilinx

JESD-30 Code: S-PBGA-B676

Number of CLBs: 2320

Number of Terminals: 676

Package Body Material: PLASTIC/EPOXY

Package Style: **GRID ARRAY**

Seated Height-Max: 2.44 mm

Supply Voltage-Nom: 1.5 V

Terminal Finish: Tin/Lead (Sn63Pb37)

Time@Peak Reflow Temperature-Max (s): 30

Pbfree Code: No 💿

Part Package Code: BGA

ECCN Code: 3A991.D

Risk Rank 8.73

JESD-609 Code: e0

Number of Inputs: 404

Operating Temperature-Max: 100 °C

Package Code: BGA

Peak Reflow Temperature (Cel): 225

Subcategory: Field Programmable Gate Arrays

Surface Mount: YES

Terminal Form: BALL

Width: 27 mm Rohs Code: O No

Package Description: BGA, BGA676, 26X26, 40

8542.39.00.01

Length:

Number of Logic Cells:

Operating Temperature-Min: -40 °C

BGA676,26X26,40

FIELD PROGRAMMABLE GATE ARRAY

1.575 V

Terminal Pitch: 1 mm

Part Life Cycle Code: Obsolete

Pin Count: 676

Factory Lead Time: 12 Weeks

Combinatorial Delay of a CLB-Max: 0.32 ns

Moisture Sensitivity Level: 3

Number of Outputs: 404

Organization: 2320 CLBS

Package Shape: SQUARE

Qualification Status: Not Qualified

Supply Voltage-Min: 1.425 V

Temperature Grade: INDUSTRIAL

Terminal Position: BOTTOM

HTS Code:

Clock Frequency-Max: 1200 MHz

27 mm

20880

Package Equivalence Code:

Programmable Logic Type:

Supply Voltage-Max:

Technology: CMOS

| Name        | Bit Index | Description                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|-------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| MATCH_CYCLE | [11:9]    | Startup cycle to stall in until DCI matches.<br>000: Startup phase 0<br>001: Startup phase 1<br>010: Startup phase 2<br>011: Startup phase 3<br>100: Startup phase 4<br>101: Startup phase 5<br>110: Startup phase 6<br>111: No Wait                                                            |  |  |  |  |  |  |  |

| LOCK_CYCLE  | [8:6]     | Startup cycle to stall in until DCMs lock.<br>000: Startup phase 0<br>001: Startup phase 1<br>010: Startup phase 2<br>011: Startup phase 3<br>100: Startup phase 4<br>101: Startup phase 5<br>110: Startup phase 6<br>111: No Wait                                                              |  |  |  |  |  |  |  |

| GTS_CYCLE   | [5:3]     | Startup cycle to deassert the Global Three-State<br>(GTS) signal.<br>000: Startup phase 1<br>001: Startup phase 2<br>010: Startup phase 3<br>011: Startup phase 4<br>100: Startup phase 5<br>101: Startup phase 6<br>110: GTS tracks DONE pin. BitGen option -g<br>GTS_cycle:Done<br>001: Keep  |  |  |  |  |  |  |  |

| GWE_CYCLE   | [2:0]     | Startup phase to deassert the Global Write Enable<br>(GWE) signal.<br>000: Startup phase 1<br>001: Startup phase 2<br>010: Startup phase 3<br>011: Startup phase 3<br>101: Startup phase 5<br>101: Startup phase 6<br>110: GWE tracks DONE pin. BitGen option -g<br>GWE_cycle:Done<br>111: Keep |  |  |  |  |  |  |  |

Table 6-10: Configuration Options Register 0 Description (Continued)

# Configuration Options Register 1 (COR1)

The Configuration Options Register 1 is used to set certain configuration options for the device. The name of each bit position in the COR1 is given in Figure 6-5 and described in Table 6-11.

| Description |        |        |        |        |        |        | Webel Aed | Recention |        |        |        |        |        |        | PERSIST_DEASSERT_AT_DESYNCH | Reserved |        |        |        | Reserved |        |        | RBCRC_NO_PIN | RBCRC_EN |   |   | Received |   |   | RPI 1ST READ CYCIES |   |   |

|-------------|--------|--------|--------|--------|--------|--------|-----------|-----------|--------|--------|--------|--------|--------|--------|-----------------------------|----------|--------|--------|--------|----------|--------|--------|--------------|----------|---|---|----------|---|---|---------------------|---|---|

| Bit Index   | 3<br>1 | 3<br>0 | 2<br>9 | 2<br>8 | 2<br>7 | 2<br>6 | 2<br>5    | 2<br>4    | 2<br>3 | 2<br>2 | 2<br>1 | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7                      | 1<br>6   | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2   | 1<br>1 | 1<br>0 | 9            | 8        | 7 | 6 | 5        | 4 | 3 | 2                   | 1 | 0 |

| Value       | 0      | 0      | 0      | 0      | 0      | 0      | 0         | 0         | 0      | 0      | 0      | 0      | 0      | 0      | 0                           | 0        | 0      | 0      | 0      | 0        | 0      | 0      | 0            | 0        | 0 | 0 | 0        | 0 | 0 | 0                   | 0 | 0 |

## Figure 6-5: Configuration Options Register 1

## Table 6-11: Configuration Options Register 1 Description

| Name                        | Bit Index | Description                                                                                          |

|-----------------------------|-----------|------------------------------------------------------------------------------------------------------|

| PERSIST_DEASSERT_AT_DESYNCH | 17        | Enables deassertion of PERSIST with the DESYNCH command                                              |

| RBCRC_NO_PIN                | 9         | Disables INIT_B as read back CRC error status output pin                                             |

| RBCRC_EN                    | 8         | Continuous readback CRC enable                                                                       |

| BPI_1ST_READ_CYCLES         | [3:2]     | First byte read timing:<br>00: 1 CCLK<br>01: 2 CCLKs<br>10: 3 CCLKs<br>11: 4 CCLKs                   |

| BPI_PAGE_SIZE               | [1:0]     | Flash memory page size:<br>00: 1 byte/word<br>01: 4 bytes/words<br>10: 8 bytes/words<br>11: Reserved |

## Warm Boot Start Address Register (WBSTAR)

The name of each bit position in the WBSTAR is given in Figure 6-6 and described in Table 6-12.